产品列表PRODUCTS LIST

一些 5G 系统的制造商正在转向更高水平的硬件集成,并在片上系统(SoC)设备中整合射频转换器和基带处理引擎,以解决功耗和电路板空间问题。虽然这种集成有好处,但负责这些系统表征的工程师面临着访问数据的新挑战,因为之前的独立射频数据转换器现在将与 FPGA 和处理器在同一芯片上进行组合。

另一个困扰工程师的因素是 5G 标准本身。作为一种新标准,5G 很可能会向前发展,因此工程师们不仅需要应对如何在集成设备中获取表征数据的变化,还需要应对参考波形和性能标准可能发生的变化。这给表征过程增加了额外的负担,它需要足够的灵活性来应对不断变化的需求。

为了能够通过 SoC 进行数据访问并应对可能不断变化的标准,理想的表征环境需要灵活的信号生成和分析能力,它不仅能够生成符合当前 5G 标准的波形,还可以随着标准的发展生成新的波形。这种信号生成和分析能力还需要能够从新的 SoC 硬件中提取射频数据,而不需要射频工程师成为 SoCs 编程方面的专家。

如果这种信号生成能力与信号捕获和分析能力包含在相同的桌面环境中,工程师可以执行许多射频测试和表征任务,而不需要传统的台式测试设备。

虚拟测试设备与传统测试设备

虽然总会有地方放置台式信号发生器、频谱分析仪和其他相关传统测试设备来验证系统性能,但是这些仪器的成本和物理尺寸使得它们在系统设计的初始表征和“假设”阶段不那么受欢迎。允许算法开发人员、射频工程师和系统设计人员访问他们的虚拟测试“实验室”可以加速设计迭代,并帮助更快地获得佳设计。

硬件和算法的不良选择可以在设计过程的早期被剔除,而不会占用昂贵的共享资源,如台式测试设备,更不会占用拥有该设备的相关测试人员。同样,在进行更广泛的测试过程之前,可以快速识别出良好的设计理念,并将其发展到更高的程度,大大提高通过认证的可能性,而无需大量的硬件返工,从而节省了开发时间和成本。

这里的目标不是取代桌面测试,而是在过程的早期添加基于软件的测试,从而降低硬件原型构建成本并提高工程生产率。

但是,这类桌面特征化环境如何与 5G 系统开发的原型硬件一起使用呢?图 1 显示了 SoC 设备的软件表征设置,该 SoC 设备由集成了可编程逻辑和基于 MCU 的处理系统的 8 通道射频 ADC 和 8 通道射频 DAC 组成。

图 1. 连接到基于 PC 的测试环境的 EFSoC 开发工具包

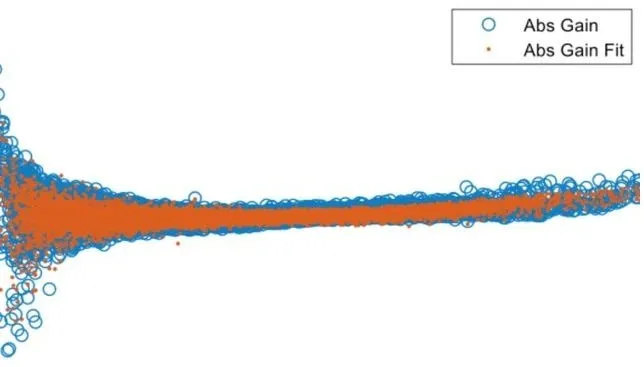

信号将通过 MATLAB 应用程序在 PC 上生成,然后发送到 Zynq UltraScale+ RFSoC 设备,输出设备的 DAC,通过 ADC 后返回 PC。基于 PC 的应用程序 RFSoC Explorer 将管理数据传输、信号生成和各种分析功能,如图 2 所示。

图 2. RFSoC 资源管理器表征描述工具的截图

这种“闭环”测试可减少对外部测试设备的需求,并允许用户将 RFSoC 上的 ADC 和 DAC 的性能表征到足以对硬件的适用性做出判定的到水平。

这种基于软件的测试方法使射频工程师能够访问嵌入 SoC 中的数据转换器,而无需对设备本身进行编程来实现数据访问,并提供信号生成所需的灵活性,允许用户在标准发展时根据需要修改波形。

扩展测试方法

虽然基于软件的测试方法能够快速做出有关适用性的决定,但也有局限性,主要是硬件和主机之间通信通道的速度和测试软件本身进行信号分析的速度。如果测试要求更快的信号分析数据速率,则可以使用相同的软件前端生成信号,将传统的测试设备连接到 RFSoC 输出端进行数据分析。这种方法仍然允许波形可编程性,同时缓解了潜在通信瓶颈的影响。

附加测试场景包括使用 RFSoC 设备上的可编程逻辑作为其自身的信号发生器,或在设备中添加逻辑以创建其自身的测试场景,例如对传入数据设置某些触发条件,并仅捕获感兴趣的数据以便在 PC 上进一步分析,而不是流式传输所有数据。

如有侵权请联系删除。